# TLM Platform Based on SystemC for Hybrid MSR Topology

Abid Noureddine<sup>1</sup>, Zitouni Abdelkrim<sup>2</sup>, Tourki Rached<sup>1</sup>

<sup>1</sup>Electronics and Microelectronics Laboratory, University of Monastir, Tunisia

<sup>2</sup>Colledge of Education in Jubail, University of Dammam, Dammam 31441, KSA

#### **Abstract**

The Network-on-Chip (NoC) Architectures have been proposed as a revolutionary methodology to the communication of multicore embedded processor in a chip. Interconnection topology plays an important role in communication locality of future CMPs. We suggest extracting the locality communication of sub tasks of applications. Indeed it is essential to provide a suitable NoC topology that exploits the locality of communication resource fully.

Due to the tradeoff between the performance and area constraint in on-chip network designs, we have developed in this paper a transactional level model NoC router of hybrid Mesh-Star-Ring. The new hybrid topology called Hybrid Locally Mesh Globally Star-Ring (HLMGSR) use the Star-Ring and mesh graphs as the basic building blocks. The experimental results show that for a network size equal to 128, the proposed hierarchical topology HLMGSR provides an area increase of 7% over the mesh. For a network size which is greater than or equal to 64 nodes, the lowest average latency is provided by the proposed hybrid topology for different injection rates. For a network size greater or equal to 64 nodes with the uniform traffic pattern with a lower injection rate, the results show that the HLMGSR provides the highest throughput.

**Keywords:** Network on chip, Hybrid NoC, Locality of Communication, TLM 2.0.

### 1. Introduction

System-on-Chip (SoC) provides single chip solutions in many applications require single or large chip implementations. To provide more computing power, designing multiprocessor system on chips (MPSoC) [1] can be used. MPSoC requires high-speed communication between processors which dependent on the fast and flexible interconnect network. Network-on-Chip (NoC) has been proposed as a promising approach for future multi-core systems, to overcome the problems of complexity and scalability of inter communication platform of SoCs composed by hundreds of cores. The interconnection topology acts an important role in communication locality inside chip multiprocessors. Many network architecture interconnections that are based on different standard topologies have been studied recently for SoC such as 2D Mesh [2], Torus [3], Fat-Tree (FT) [4], Ring [5], Butterfly-Fat Tree (BFT) [6], Spidergon [7], Octagon [8]. These architectures are based on parallel concepts and distributed systems for interconnecting resources in a structured and scalable manner for ease of implementation.

The 2D-Mesh topology [3] is a popular topology used for NoC interconnects because of the regularity, the low complexity, and planer 2D layout properties. However, the large network diameter, suffers from large hop count that can increase the communication latency packets. The ring topology is characterized by the simplicity of its structure, lower average latency and high bandwidth. The ring topology has larger hop count with larger network diameter. However, the scalability of the ring topology can be limited [9].

The high performance parallel processing domain therefore admits very high dimensional and complex topologies that can greatly reduce its communication costs and improve its performance. Indeed, high-dimensional hyper-cubes are popular due to their ability to easily embed other problems [10].

The Star-Ring NoC topology [11] is a mixture of Ring and star topology. It was developed to fulfill the demands for the communication structure in the area of high performance computing. Therefore, it features a high throughput and a low latency.

Many architectures based on tiled exist ranging from Chip Multi-Processors (CMPs) to arrays of programmable logic or even to heterogeneous arrays that include custom-IP blocks.

Future massively parallel CMPs, will execute applications with enormous amounts of parallelism. We can have applications with significant amount of parallelism, or locality of communication, or both.

The mapping algorithm must also favor the locality of communication minimizing critical paths and congestion by using many sub-networks for local communication and one network for global communication. An application mapped on Network on chip based on such hybrid topology provides much higher bandwidth and lower-latency communication channels available between cores on chip. To further optimize NoC performance, it is expected that a combination of the benefits of different well established methodologies as such as a mesh, star,

ring, bus and point-to-point topology can provide benefits of both.

In this paper, we propose a new hybrid topology that can be personalized by the combination of the benefits of the 2D-Mesh, STAR and RING architectures MSR.

Our objective is to design a hybrid locally Mesh globally Star-Ring (HLMGSR).

The transaction level modeling methodologies has been proposed as a way to tackle firstly the HW/SW co-design problems and secondly the early architecture analysis [12]. To study the proposed topology in detail, we have developed a transaction level model of communication components of NoC such as link, routers which is implemented in SystemC TLM2.0. By integrating functions to calculate latency and throughput of interconnection architecture in addition to communication functions we were able to compare the performance characteristics of our hybrid interconnect where a large mesh is broken into smaller meshes, globally connected by a STAR-RING hybrid topology for routing global traffic.

### 2. Related works

www.IJCSI.org

In order to find a tradeoff between the resource requirements and system performance in term of surface, reduced hop counts and throughput, a new Network on Chip topologies has been proposed such as hierarchic and hybrid topologies. These networks has been proposed and compared in terms of latency, throughput, and energy dissipation [13], [14].

In [15], an optimal Network on Chip topology which uses the star graphs has been proposed as building blocks. It uses a hierarchical star topology based on star graph. Compared to many topologies in the same category in terms of various performance metrics (diameter, cost, fault tolerance, fault diameter), the hierarchical star topology showed the most energy-efficient and cost-effective topology.

To reduce the latency of long distance traffic in normal mesh 2D, a STAR-TYPE architecture [16] topology has been proposed. It consist to divide an original mesh to 3x3 sub mesh connected together at the central node forming the star topology to form the second-level mesh and using a simple routing algorithm with deadlock-free routing. Compared to normal mesh 2D, the proposed topology presents a good improvement in terms of hop-count reduction which can reach 60, 87% but the drawback of star type architecture is that it consumes more power and area of 34.27% and 57.54% respectively.

A Generic and Extensible SPIDERGON NoC has been proposed in [17]. It is based on elementary asynchronous SPIDERGON network which is a combination of the star

and the ring architectures. The set of elementary Spidergon networks are organized as a two order matrixes. The proposed architecture is characterized by the lower latency and the later saturation, but it suffers from it's over costs in terms of silicon area.

The Proteo [18] Network on Chip is divided into clusters, using a hierarchical network. It comprises multiple subnets with different performance, topologies and packet formats. The hierarchical network built from a system-wide bidirectional ring and several subnets with star (or bus) topology.

In order to smooth and evenly distribute the flow of communication traffic, Ring Road [19] topology has been proposed to avoid congestion in the center by forcing some traffic to take a detour around the center, using ring switching elements to provide more bisectional bandwidth. To reduce energy consumption, authors in [20], benefited from the scalability, modularity, and energy efficiency of hierarchical ring. Two-level hierarchical ring interconnect was modeled and evaluated for SoC multiprocessor systems. This topology was inspired by a NUMAchine multiprocessor described in [21]. The proposed multi processors NUMachine uses a hierarchical ring based interconnect. This architecture is composed by local and central rings that are joined by inter-ring interface allowing the construction of a modular system with parallel computing capability and cost efficient feature. In [22] through the proposed hybrid Mesh based Star topology an improvement of throughput and low hop count latency was shown compared to SD2D [23], L2STAR [24] and original mesh.

To benefit it from the advantage of mesh topology for short distance traffic, and the advantage of star topology for long distance traffic, author in[25] has proposed a 2D Hybrid Mesh based on Star topology to connect locally mesh and globally star. The proposed architecture improves system performance in term of maximum latency of 62% and increase of 48% in throughput compared to simple 2D mesh under static routing.

In [26] a scalable and heterogeneous NoC with Star-Wheels topology has been proposed which combine the star topology with the Wheel topology (star and the Spidergon topology) utilizing packet switching for controlling data and circuit-switching for an image processing application.

To overcome the problem of Mesh topology, a large communication radius and hot spots have been developed in the center of the Mesh. Authors in [27] have proposed a hybrid ring/mesh architecture, which use a large mesh topology partitioned into smaller sub-meshes for local routing and a hierarchical ring interconnect for global routing of smaller sub-meshes.

For high performance network-on chip, A Scalable hierarchical architecture based Code-Division Multiple

Access (CDMA) has been proposed in [28]. A large network can be obtained, by scaling the local switch architecture. This work is based on CDMA switch in the center for the uncast and multicast data between the IPs blocks. This architecture has presented an average

improvement of 24.2% in area cost with a reduction of 25% in the power consumption compared to the conventional design.

In [29], a multicast network-on-chip has been proposed using a combination of hierarchical star and ring topology to support a real-time object recognition processor that supports less than 3 switches hop latency. The proposed architecture has shown an improvement in term of data transaction time and energy consumption by 20% and 23%

respectively.

www.IJCSI.org

In [30], a hybrid mesh-ring topology has been proposed. It consists of some local mesh networks connected together through a global ring network. Each type of network includes a monitoring system to balance the network load over the communication resources by observing traffic in the network and delivering traffic information to the routers.

To provide the communication of multiple processor elements with high computing performance, a novel hybrid topology STAR- Wheel was proposed in [26]. Both packet switching and circuit-switching were used as communication protocol for data control and data application respectively.

A new NoC with hybrid topology has been proposed in [32]. It is a hybrid of mesh, torus and folded torus. The proposed topology consists of three kinds of links, torus links, folded torus links, and mesh links with a uniform router. However, a significant reduction of the number of average hops-count and an increase of throughput compared to mesh, torus and folded torus topologies was presented.

To provide low latency, higher throughput, and good balancing load network, a 2D hybrid mesh based star topology has been proposed in [25]. by using two different types of connections at different levels, the proposed topology facilitates both long distance traffic and short distance traffic and has presented an improvement of low latency and an increasing throughput by 62% and 48% respectively compared to simple mesh2D.

To reduce the communication overhead for performance, we propose an approach to restrict the communication to a small set of nodes. To enhance the throughput using dedicated local connections, we suggest in this work a new hybrid topology that integrates the 2D-Mesh, STAR and RING architectures benefiting from the advantage of such communication locality. We identify a hybrid locally mesh globally Star-Ring HLMGSR topology and we evaluate it in terms of throughput, latency and area, at the transactional level with SystemC TLM2.0. The hybrid

topology HLMGSR uses the Star-Ring and mesh graphs as the basic building blocks, and inquires about the topological characteristics of the resulting family of networks.

### 3. Topology Exploration

The topology selection in the design of NoC presents a major preoccupation for its importance in the determination of the structural organization of the network routers and subsequently the evaluation of performance in terms of average latency, the total bandwidth and the implementation roughly cost.

The popular 2D-mesh topology has strength in regularity, scalability and fault tolerance due to link failure. However, it suffers from high transmission latency when the network size increases. On the other hand, the star topology performs well for smaller diameter networks. It can also lead to short average hop distance. In opposition, it represents a bottleneck communication in the center node due to congestion [16].

The ring topology that is characterized by its small degree, show that every node has two neighbors however, the since increasing linearly of its diameter lead to long hope latency. In this work, we try to combine these topologies together in order to benefit from advantages of each topology.

We present a new hybrid Mesh Star-Ring combined topology architectures called HMSR (Hybrid Mesh Star-Ring). HMSR is a hybrid interconnected topology which connects localized subnets with each other via global routers. HMSR use multiples mesh as local networks and use one star-ring topology as global network (LMGSR).

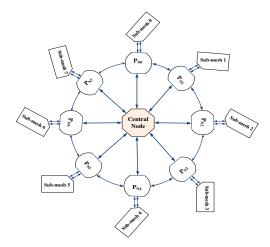

Fig. 1. Hybrid Local Mesh Global Star-Ring topology

# 3.1 HLMGS: Hybrid Locally Mesh Globally Star-Ring topology

www.IJCSI.org

CCW or CA.

The hybrid LMGSR NoC is a communication structure for integrating a very high number of multiple cores and providing highly flexible connectivity at the necessary time. It consists of a local mesh as a subnet and a global Star-Ring network which connects the local sub-meshes as can illustrated in figure 1. Four IPs are attached to four Local Switches (LS) in each subnet and the local switch is connected to one Global Switch (GS).

The router coordinate (0, 0) in the corner of each subnet operates as a router of the mesh to route packets inside the mesh. It also provides the link between these global routers. The corner routers are directly connected to the peripheral Routers of star-ring topology.

The proposed global Star-Ring (SR) topology [11], that is based on star topology adds ring topology for short latency data transmission from the start IP that allow the reduction of the hop count of global long distance traffic. It's characterized by a diameter of two links regardless of its size. The SR Network is scalable in a way that the number of subnet as well as the number of resources on a subnet can be easily increased. It has three channels so that the packets can be transferred in three directions CW,

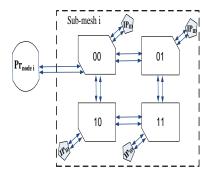

We consider for instance 4x8 mesh topology that supports 32 IP has been divided into eight 2x2 sub-meshes which are globally connected using Star-Ring architecture. Each IP is attached to each local sub-meshes switch (LS). The Local Switch (LS) coordinates (0, 0) in the corners of each sub-meshes is connected to one single global switch (GS) and operates as switches of local sub-meshes network as well as a router to construct a second-level sub-meshes. The structure of the subnet is presented in Figure 2.

Fig. 2. Local mesh Subnet

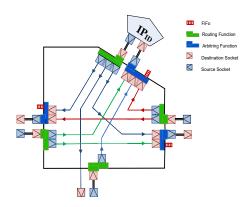

Regardless of the type of architecture, Network on chip topologies can be described by a graph G (R, C), where R is the set of routers, and C is the set of channels between switches [10]. The standard router utilized in the

modulation of different topologies, consists of a routing module, two buffer elements on each channel which receive packets and send them forward as shown in figure 3. The routing module is modular in a way that the arbitration method and the routing algorithm can be modified on the function of local subnet size.

In the new HLMGSR topology, R includes local switches (LS) that provide the intra-subnet switching and global switch (GS) for inter-subnet switching.

The number of core (IPs) can be increased linearly depending on the size of local subnet, where M and N represent the width of sub-mesh and J is the number of global switches on the SR topology.

The number of cores (IP) is calculated by equation (1).

$$Core_{LMGSR} = M \times N \times J \tag{1}$$

The number of routers in Star-ring topology V (Star-Ring valence) is calculated using equation (2).

$$V = star - ring \ valence + 1$$

(2)

Fig. 3. Internal connectctivity of periphiric router

The number of routers (switches) K in HLMGSR topology is calculated using equation (3)

$$K = [(star - ring \ Valence \times (M \times N) + 1)]$$

(3)

The Min hop count number in HLMGSR topology is calculated using equation (4).

$$Min - HP = \left[ \left( M + N \right) - 2 \right] \tag{4}$$

The max hop count number in HLMGSR is calculated according to equation (5) independently of IP core number

$$Max - HP = \left[ \left( M + N \right) - 2 \right] + 2 \tag{5}$$

### 3.1.1 HLMGSR Addressing

In order to transmit packets of IP cores across the NoC, a unique address must be assigned to each reachable

destination. In both network levels, switches just like IP core have their own unique address as following.

www.IJCSI.org

- Source mesh node Address SmNA= (Xs, Ys)

- Destination mesh node Address DmNA= (Xd, Yd)

- Source Star-Ring node Address SSRA= (Ns)

- Destination Star-Ring node Address DSRA= (Nd)

- Distance in X dimension between current node and Destination node  $\Delta x = Xd Xs$

- Distance in Y dimension between current node and Destination node Δy = Yd - Ys

- Distance in global dimension between current SR node and destination SR node:  $\Delta G = Gd Gs$

- the identification in the global system: id

$$IP_{id} = (m \times n \times Nod_{Star-Ring}) + (X \times m + Y)$$

(6)

# 3.1.2 Proposed HLMGSR routing algorithm

In the proposed routing algorithm, each router node position in HLMGSR topology is represented by (X, Y, Gx ) , where X and Y represent the row and column number of specific local node and Gx represents the source or destination global address of a particular node in a global system.

$\Delta G$ ,  $\Delta x$  and  $\Delta y$  have been used to measure the difference between the source and destination node. When  $|\Delta G|$  are equal to zero, the packet follow local routing, else it follows global routing.

To travel locally, the HLMGSR NoC uses a deterministic X-Y routing on the local sub-meshes networks. Each router on sub-meshes can be identified by its coordinate (x,y). The X-Y algorithm compares the source router address to the destination router address of the packets presented by  $\Delta x$  and  $\Delta y$ .

If  $\Delta x$  and  $\Delta y$  are equal to zero, the packet must be routed to the local port. If this is not the case, the Xd address is firstly compared to Xs address then the packet will be routed to east or west port when XS < Xd or XS > Xd respectively and if XS = Xd.

In the second level, Yd Address is compared to YS address. The packet will be routed to south when YS<Yd, to north when YS>Yd.

To send a packet from an initiator to a target connected to remote sub-meshes, the X-Y routing algorithm tends to route global traffic away from the IP sender to the corner router (0, 0) which represents a bridge between the local and global traffic.

When the difference between the source and destination node at global network are not equal to zero  $|\Delta G| \neq 0$ , the packet must follow the global routing. In the global network level, a determinist routing algorithm is adopted while ensuring a communication cost less than or equal to 2 hops regardless of the network size and the STAR

valence. The communication cost is given by the following expression:

min [ f (way1), f(way 2)]  $\leq$  2, where **f** is the cost function in number of links.

The pseudo code of the proposed routing algorithm is as follows:

```

If (|\Delta G| = 0)

{//packets travelling on local sub-mesh with XY algorithm

If (\Delta x > 0 \text{ and } \Delta y > 0) then go to ES;

Else if (\Delta x > 0 \text{ and } \Delta y = 0) then go to S;

Else if (\Delta x > 0 \text{ and } \Delta y < 0) then go to WS;

Else if (\Delta x = 0 \text{ and } \Delta y > 0) then go to E;

Else if (\Delta x = 0 \text{ and } \Delta y = 0) then go to Local;

Else if (\Delta x = 0 \text{ and } \Delta y < 0) then go to W;

Else if (Dx < 0 \text{ and } Dy > 0) then go to EN;

Else if (\Delta x < 0 \text{ and } \Delta y = 0) then go to N;

Else if (\Delta x < 0 \text{ and } \Delta y < 0) then go to WN;

End if;

Else packets travelling on global Star-Ring algorithm;

End if:

If (|\Delta G| \le 2)

{//-- the global routing algorithm

If |\Delta G| < 0 then go to clockwise direction;

Else if |\Delta G| > 0 then go to counter clockwise direction;

Else if (|\Delta G| = 0 \text{ and } \Delta x = 0 \text{ and } \Delta y = 0) then go to local of

destination sub-meshes corner routers;

End if:

```

Else go to the central router in the across direction to reach the destination star-ring routers; End if:

# Pseudo-code of the Proposed Algorithm

# 3.1.3 Deadlock avoidance

A deadlock can occur in NoC when different packets will wait for each other for undefined time in a cyclic way [32]. In this study we use deterministic XY routing for local routing, which is a deadlock-free routing algorithm.

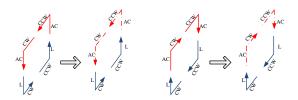

For global routing, the problem of infinite waiting path for wormhole routing can occur during the even cycle such as the example of routers 0, 1, and 8 which can communicate together Prohibiting certain turns in global network, we can avoid this kind of deadlock.

The routing algorithm would be to prohibit at least one turn in each of some possible cycles in the network. Thus, it can avoid a path between each pair of nodes as illustrated in figure 5, but it should not prohibit more laps than necessary, Interruption of communications, manifested by prohibiting turns CW-AC and CCW-AC.

As shown in Figure 4 for the steps of value 1 or 2, the decision function returns a value less than or equal to 2 for calculating the cost of communication intra-ring and inter-Ring. On the other hand, with steps values greater than two, the routing is done through the central node

www.IJCSI.org

S0 $\rightarrow$ to D1. First way (0, 8, 1), f (way1) =2. Second way (0, 1), f (way 2) = 1. Min [f (way 1), f (way 2)] =1.

S0 $\rightarrow$  D2, First way (0, 8, 2), f (way1) =2. Second way (0, 1, 2), f (way 2) = 2. Min [f (way 1), f (way 2)] =2.

S0 $\rightarrow$  D3, First way (0, 8, 3), f (way1) =2. Second way (0, 1, 2, 3), f (way 2) = 3. Min [f (way 1), f (way 2)] =2.

Fig. 4. Some scenarios for finding shortest path length with maximal diameter 2

The separation of the communication inter-ring and intraring does not allow recovery the deadlock and live-lock problems. Each packet from an input port device in the central node will be able to be routed throughput ports where it represents the valence of the network.

### 4. Experimental results and discussion

Using N routers scales for classical mesh and proposed hybrids topologies as shown in figure 1 some structural characteristics are analyzed. They comprise degree, diameter, hop count, average minimum hop count, average latency and ideal throughput, and further performance evaluation using TLM2.0.

Fig. 5. Showing deadlock avoidance scheme model

### 4.1 Structural proprieties

### 4.1.1 The degree of the topology

The degree of the topology is the maximum number I/O links associated with the network nodes reflecting the complexity of the topology [15]. The degree of the proposed hybrid topology has uniform degree of all switches except the central node of starring topology which may vary depending on the network size. The maximum degree of the hybrids topologies is limited to 5.

### 4.1.2 Network diameter

The reduction of network diameter allows the decrease of communication overhead. The network diameter is defined by the largest minimal hop count over all node pairs communicating in the NoC Topology with N node.

$$H_{\text{max}} = \max H(s,d) \tag{13}$$

The diameter of MxN mesh network is (M+N)-2; for the proposed hybrid topology HLMGSR is 4+2 [(M+N)-2] Minimizing the diameter of the network topology in our hybrid network essentially depends on the choice of the locally Mesh network.

The diameter of hybrid topology HLMGSR can decrease by 25% and compared to mesh topology.

### 4.1.3 Ideal average latency

www.IJCSI.org

The time required for a packet to traverse the network from source to destination without any congestion in routing is called ideal average latency. This latter can be estimated in formula (14) [33].

$$A_{v} latency = A_{rd} + \frac{D}{v} + \frac{L}{b}$$

(14)

$A_{rd}$  is the average router Delay which depends on the average minimal hop count  $H_{min}$  and the delay of single router Tr,(cycle/hop), knowing that Tr essentially depend on the physical implementation of the router and the routing algorithm.

$$A_{rd} = H_{\min} \times T_r \tag{15}$$

The ratio between the average distance D from source to destination (hop) that is usually equal to  $H_{\text{min}}$ , and wire transmitted speed v(hop/cycle) represent the transmission time for a network.

The required time to cross a packet of length L(flit/cycle) via a channel with bandwidth b is a ration L/b.

The average minimum hop count of a network represents the average of all possible paths between two node source and destination sources.

$$\boldsymbol{H}_{\min} = \frac{1}{N^2} \sum H(s, d) \tag{16}$$

Tableau 1: calculation of the minimum hop count

| Topology | 32   | 64   | 72   | 128  |

|----------|------|------|------|------|

| Mesh     | 3,87 | 5,25 | 5,58 | 7,93 |

| HLMGSR   | 5,12 | 6,96 | 6,97 | 8,81 |

The average minimum hop count of N node network varies depending on the larger networks and calculating similarly for the compared topology knowing that each node is considered as source and destination.

The decrease of  $H_{\text{min}}$  becomes interesting from network size of 70 nodes. The  $H_{\text{min}}$  of HLMGSR is 39% less compared to Mesh at 128 node larger network. While the HLMGSR brought no improvement in term of average minimum hop count.

Assuming a typical 5-stage pipeline router used with the interval time between adjacent pipeline stage is 1 cycle, tr = 4 cycle/ hops, V = 1flits/cycles, L = 2 flits and b = 1flits/cyle. Therefore, the ideal average latencies of Meshes and the proposed hybrid topology are shown in table 2

Tableau 2: calculation of the ideal average latency

| Topology | 32    | 64    | 72    | 128   |

|----------|-------|-------|-------|-------|

| Mesh     | 21,35 | 28,25 | 29,57 | 41,65 |

| HLMGSR   | 27,6  | 36,8  | 36,85 | 46    |

We Remarque that the ideal average latency of hybrid Mesh is less than the HLMGSR topology by average of 28%, but at 128-node scale, the difference of average latency between Mesh and proposed HLMGSR topology decreased at 10%.

### 4.1.4 Ideal Throughput

Adopting the bisection parameter of network (eq. 17) we can estimate the ideal throughput of a topology, determining the maximum throughput in a perfect flow control and routing mechanism [32].

$$T_h \le \frac{2 \times b \times B_c}{Nodes \ numbers} \tag{17}$$

$B_{\rm c}$  is the channel count required to portioning the network nearly in half b is the width of a network.

Tableau 3: calculation of the ideal throuput

| Topology | 32    | 64     | 72   | 128    |

|----------|-------|--------|------|--------|

| Mesh     | 0,5b  | 0,5b   | 0,4b | 0,25b  |

| HLMGSR   | 0,75b | 0,375b | 0,3b | 0,187b |

The ideal throughput of hybrid topology HLMGSR is characterized by a slightly throughput stability compared to the mesh, when increasing the network scales.

Tableau 4: performance comparison against Mesh topology (128 nodes)

| Topology | Average Minimum Hop<br>Count |        | Idial<br>Throughput |

|----------|------------------------------|--------|---------------------|

| HLMGSR   | +11%                         | +10,4% | +33%                |

The performance comparison of proposed hybrid topology at 128 nodes is illustrated in Table 4. The Average minimum hop count is rised by 11% for the HLMGSR topology when compared to Mesh. The average latency is increase by 10,4% for the HLMGSR when compared to Mesh topology. The best throughput of hybrid topology HLMGSR increases by 33% when compared to mesh architecture.

#### 4.2 Cost and Performance evaluation

In this section the synthesis results will be presented, and a cost analysis of area will be made based on the synthesis results. The proposed hybrid topology performance will be evaluated in terms of latency, and throughput.

The first implementation of NoC uses a HLMGSR topology. The second uses the Mesh topology. It use a network interfaces with 32 bit AHB data fields and 32 bit network ports.

The proposed topology has been modeled with VHDL language at RTL level in order to estimate the cost in term of area. It was simulated and synthesized respectively by using the ModelSim tool and Synopsys Design Vision tool.

www.IJCSI.org

Fig. 6. Comparison area cost of NoCs Architectures

We synthesized the proposed hybrid networks topology using cell based design with ST 0.13nm CMOS technology using the High Speed (HS) library. Furthermore, due to the high pin count, the experimental results are based on the circuit simulation of the design instead of the manufactured chip. The synthesis result of these networks was done with the utilized FIFO have a depth of 4 words of 32 bits. Each FIFO has an adjustable depth and width. Figure 7 shows the area of the three implementations with different network sizes (number of IP cores).

For a network size greater than 72, the area occupied by the HLMGSR network is the most reduced compared to mesh topology. The area increase is about 7% between HLMGSR and Mesh topology.

To complete the performance evaluation, a baseline routers of the Mesh, HLMGSR has been modeled with systemC TLM (transaction level modeling) [20], using an object-oriented style. The library used has been described as a network switch, communication socket, and network wrapper to evaluate the topology in terms of latency, throughput, and area. Plugging building components together provides a way for automatic generating of standard or new hybrid topology with different sizes.

The aim is to evaluate whether the average latency and the throughput for our presented hybrid topology are significantly reduced and increased respectively compared with that of Mesh. We show also that the hybrid topology is able to adapt to a variety of pattern traffic and support different number of IP cores.

We compared the proposed hybrid topology with standard Mesh in terms of latency and throughput with different injection rate, different network sizes and different traffic patterns. The number of IP core used determines the size of network that can be used for mapping the application target to NoC. We proposed to evaluate the presented topologies for different network sizes (32, 64, 72, and 128). The sub network SR is fixed with valence equal to 8. For HLMGSR topology, we used 8 mesh sub network for local communication with different sizes 2x2, 4x2, 3x3, 4x4 to construct respectively 32, 64, 72, and 128 sizes. For Mesh topology, we use 4x8, 8x8, 8x9, and 16x8 to construct respectively 32, 64, 72, and 128 sizes. For performance evaluation, we used the two most traffic patterns used in

the literature such as uniform traffic (UT) and transpose traffic (TT) for different injection rates (0,1; 0,7; 1) and we expect applications to lie in between these two traffic patterns. Figure 7 (a-f) shows the histogram of the average latency of the two topologies for various network sizes. We tried out three injection rates 0,1; 0,7 ;1 (packet/node/cycle) respectively correspond to the subgraph (a), (b) and (c) for the transpose traffic patterns and (d), (e) and (f) for the uniform traffic patterns.

From the histogram, it is clear that for the transpose traffic and for a network size lower than 64 nodes, the Mesh topology provides the lower average latency for the different injection rates.

Average Latency under transpose Average LatencyunderUniform traffic traffic

**a.**Injection rate= 0.1(packets/node/cycle)

rate=

**b.**Injection 0.7(packets/node/cycle)

**e.**Injection rate=0.7(packets/node/cycle)

**c.**Injection rate= 1/packets/node/cycle

**f.**Injection rate= 1/packets/node/cycle

Fig. 7. Latency versus injection rate obtained by uniforme and transpose traffic

rate=

It is also clear that for uniform traffic and for a high injection rate, the Mesh topology provides the lowest average latency. For lower injection rate, and for a network size lower than 64 nodes, the HLMGSR topology provides the lowest average latency.

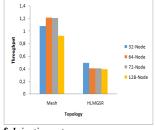

Figure 8 shows the histogram of the throughput of the two topologies and various network sizes. We experimented with three injection rates for the two traffic patterns.

Throughput under transpose traffic

www.IJCSI.org

Throughput under Uniform traffic

**d.**Injection rate= 0.1/packets/node/cycle

**b.**Injection rate= 0.7(packets/node/cycle)

**e.**Injection rate=0.7(packets/node/cycle)

c. Injection rate= 1/packets/node/cycle

**f.** Injection rate= 1/packets/node/cycle

Fig. 8. Throughput versus injection rate obtained by uniforme and transpose traffic

It is clear from the histogram, that for a network size greater or equal to 64 nodes with the transpose traffic pattern, the best throughput is provided by the HLMGSR for different injection rates.

For higher injection rate the HLMGSR provides the highest throughput.

### 5. Conclusion

In this work, we investigate communication locality between MSR and 2D mesh. we have presented a new hybrid topology Hybrid local mesh global star-ring (HLMGSR) with the shortest path routing algorithm.

We evaluated and compared the hybrid topology against mesh NoC topology for various network sizes and workloads. The experimental result show that for a network size equal to 128, the proposed hierarchical topology HLMGSR provides an area 7% over the mesh. For a network size greater or equal to 64 nodes, the lowest average latency is provided by the proposed hybrid topology for different injection rates. The results show that for a network size greater or equal to 64 nodes with the uniform traffic pattern with a lower injection rate, the best throughput is provided by the HLSRGM, but for higher injection rate the HLMGSR provides the highest throughput.

To conclude, this paper aims at designing communication locality aware hybrid networks that the performance of a hybrid topology can be improved further by making use of more intelligent schemes for preserving locality in large SoC systems.

### References

- [1] L. Binini, G. Micheli, "Networks on Chips: A New SoC Paradigm", January 2002, pp. 70-78.

- [2] A.Brahim, Z. Abdelkrim, C.Wissem And T. Rached, "A Modular A Modular Network Interface Design and Synthesis Outlook", International Journal of Computer Science and Issues IJCSI, vol. 9, 2012.

- [3] W.Dally and B.Towles, "Route packets, not wires: On chip interconnection networks", DAC, 2001, pp.683–689.

- [4] P.P.Pande, G.De.Micheli, C.Grecu, A.Ivanov, R.Saleh, and, "Design, synthesis, and test of networks on chips", IEEE Design and Test of Computers, 22 (2005), pp. 404–413.

- [5] L.Bonon and N.Concer, "Simulation and analysis of network on chip architectures: ring, spidergon and 2D mesh", DATE, 2006, pp.154-159.

- [6] P.Guerrier and A.Greiner, "A generic architecture for onchip packet switched interconnections", DATE Proc, 2000, pp. 250–256.

- [7] M.Coppola, R.Locatelli, G. Maruccia and A. Scandurra "Spidergon: a novel on-chip communication network", International Symposium on System-on-Chip, 2004, pp. 250–256.

- [8] F.Karim, A.Nguyen, and S.Dey, "An interconnection architecture for networking systems on chip", IEEE Microprocessors, vol.22, 2002, pp. 36-45.

- [9] J. Kim and H. Kim, "Router micro-architecture and scalability of ring topology in on-chip networks", Network on Chip Architectures, 2009.

- [10] L. B. Enini and G. D. MIcheli, "Networks on Chips: Technology and Tools", place: Elsevier Morgan Kaufmann Publishers, 2006.

[11] A. Noureddine, C. Wissem, A. Brahim and Z. Abdelkrim, "A modular and generic router TLM model for speedup network-on-chip topology generation", Systems, Signals & Devices (SSD), 2013.

www.IJCSI.org

- [12] D. Greenfield, "Communication Locality in Computation: Software, Chip Multiprocessors and Brains", Ph.D.thesis, Computer Laboratory, University of cambridge, Trinity Hall,

- [13] A.Brahim, Z. Abdelkrim, C.Wissem And T. Rached, "A Stoppable clock based Approach for Low Power Network Interface Design in a Network on Chip", International Journal of Computer Science and Issues IJCSI, vol. 10, 2013.

- [14] P. P. Pande, C. Grecu, M. jones, A. Ivanov, and R. Saleh "Performance evaluation and design trade-offs for networkon-chip interconnect architectures", IEEE Transactions on Computers, vol. 54, 2005, pp. 1025-1040.

- [15] Z. Song, G. Ma, and D.Song, "Hierarchical Star:An Optimal NoC Topology for High-Performance SoC Design ", Computer and Computational Science, 2008, pp. 158-163.

- [16] K. J. Chen, C. H. Peng, and F. Lai, "Star-type architecture with low transmission latency for a 2D mesh NOC", Circuits and Systems (APCCAS), 2010.

- [17] Z. Abdelkrim, Z. Mounir, B. Sami and T. Rached, "A generic and extensible spidergon NoC ", in Proceedings of the World Academy of Science, Engineering and Technology, vol. 31, 2007, pp. 14-19.

- [18] D. S. Tortosa , J. Nurmi, "proteo: a new approach to network on-chip", in proceedings of IASTED international conference of communicationsystem and networks, 2002, pp. 55-57.

- [19] H. Samuelsson, S. Kumar, "Ring road NoC architecture", Norchip Conference, 2004.

- [20] S. Bourduas, B. Kuo, Z. Zilic, and N. Manjikian, "Modeling and evaluation of an energy-efficient hierarchical ring interconnect for Systemon-Chip multiprocessors", Circuits and systems, 2006.

- [21] R Grindley and al, "The Numachine Multiprocessor", International Conference on Parallel Processing, 2000, pp.

- [22] T. S. Das, P. Ghosal, S. P. Mohanty, and E. Kougianos, "A performance enhancing hybrid locally mesh globally star NoC topology", the great lakes symposium on VLSI, 2014, pp. 69-70.

- [23] P. Ghosal and T. S. Das, "Network-on-chip Routing Using Structural Diametrical 2D Mesh Architecture", International Conference on Emerging Applications of Information Technology (EAIT), 2012.

- [24] P. Ghosal and T. S. Das, "L2STAR: A Star Type Level-2 2D Mesh Architecture for NoC", Asia Pacific Conference on Postgraduate Research in Microelectronics & Electronics (PRIMEASIA), 2012.

- [25] T. S. Das and P. Ghosal and, "A provably good performance centric NoC topology", Microelectronics and Electronics (PrimeAsia), 2013.

- [26] D. Gohringer, B. Liu, M. Hubner, J. Becker "Star-Wheels Network-on-Chip featuring a self-adaptive mixed topology and a synergy of a circuit - and a packet-switching communication protocol", Field Programmable Logic and Applications, 2009.

- [27] S. Bourduas and Z. Zilic, "A Hybrid Ring/Mesh Interconnect for Network-on-Chip Using Hierarchical Rings for Global Routing", Networks-on-Chip, 2007.

- [28] Ahmed A. El Badry and Mohamed A. Abd El Ghany, " A CDMA based scalable hierarchical Architecture for Network-On-Chip" , International Journal of Computer Science and Issues IJCSI, vol. 9, 2012.

- [29] J. Y. Kim, J. Park, S. Lee, M. Kim, J. Oh and H. J. Yoo "A 118.4 GB/s Multi-Casting Network-on-Chip With Hierarchical Star-Ring Combined Topology for Real-Time Object Recognition", IEEE Journal of Solid-State Circuits, vol. 45, 2010, pp. 1399 - 1409.

- [30] V. Rantala, T. Lehtonen, P. Liljeberg, and J. Plosila "hybrid NoC with Traffic Monitoring and Adaptative Routing for Future 3D Integrated chips", Design Automation Conference DAC, 2008.

- [31] SandeepGopi, Rajkumar, Lakshminarayanan, and Seok-BumKO K Swaminathan, "A novel hybrid topology for network on chip", Electrical and Computer Engineering (CCECE), 2014.

- [32] A. V. de Mello, L. OST, F. G. MORAES, and N. Calazans, 'Evaluation of routing algorithms on mesh based NoCs", PUCRS, Av. Ipiranga, 2004.

- [33] W. Dally, and B. Towles, "Principles and Practices of Interconnection Networks", place: Elsevier Morgan place: Elsevier Morgan Kaufmann Publishers, 2003.